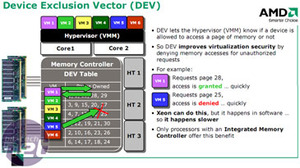

Device Exclusion Vector (DEV)

A DEV table exists within the memory controller and lets the Hypervisor (Virtual Memory Management – VMM) know if a device is allowed to access a page of memory or not. If a request arrives from a virtual OS it consults the table to determine associated memory addresses and denies it access if it doesn’t correspond to the allowed range.Not only does it improve security by having it all in hardware, it also improves performance. In contrast, Intel Xeon processors do this in software because of the separate Memory Controller Hub (MCH).

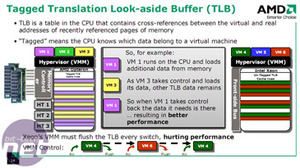

Tagged Translation Look-aside Buffer (Tagged TLB)

In relation to DEV, TLB is another table that contains cross-references between the virtual and real addresses of recently referenced memory pages. By tagging these, the CPU knows which addresses belong to which specific virtual machine. With just a single virtual machine running, the CPU doesn’t really have to worry much, but with subsequent virtual machines running the CPU needs to differentiate between them and real memory addresses.By keeping the tagging information within the TLB Cache, this means multiple VMs switching will still quickly know which address is associated with which VM. In contrast, the current Intel Xeons don’t include tagging within the TLB and with every VM change the TLB has to be flushed and repopulated, hurting performance.

This wasn’t too much of a problem before, since multiple VMs were rare in a few core environment, but with the introduction of quad core allowing 4/8/16 way servers far easier and cheaper, this means multiple environments from many users should become far more popular.

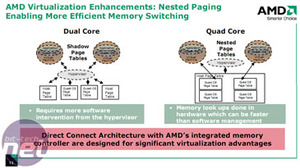

Trinity

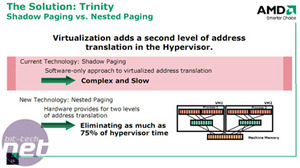

No, AMD doesn’t allow you to crack the Matrix. Yet. And you don’t get a free Carrie-Anne Moss with every purchase either. Instead this is AMD's codename for Nested Paging in a virtualised environment.Nested Paging is a far more efficient memory switching technology than the traditional Shadow Paging mechanism. Instead of constantly going through the native Hypervisor software to check Shadow Page Tables before accessing Guest OSes, Nested Page Tables are held inside the integrated memory controller, allowing the CPU to negate the software interaction before accessing a Guest OS.

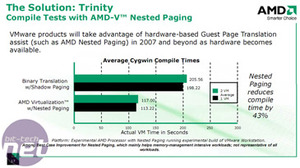

AMD quotes as much as a 75% reduction in Hypervisor access amount by running Nested Page Tables, however it wholly depends on the intensity of workloads and memory accesses between Guest OSes. Software also needs to be designed to make use of it, of which there is nothing currently available although VMWare already has working builds in the production process.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.